## MIPS processor continued

#### Review

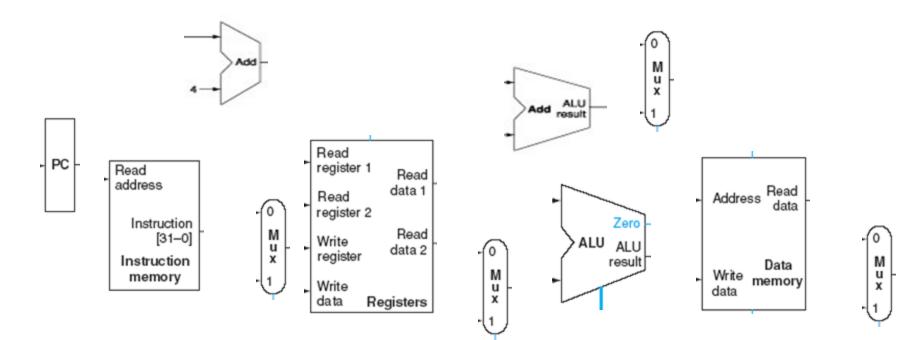

- Different parts in the processor should be connected appropriately to be able to carry out the functions.

- Connections depending on what we need

- Learnt R-type, lw, sw, beq

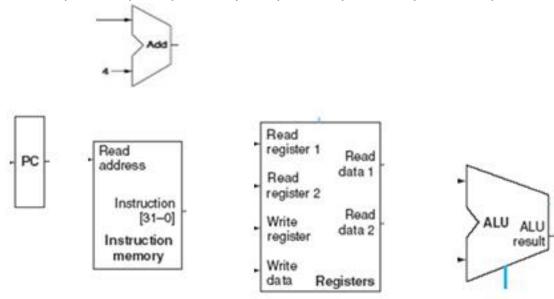

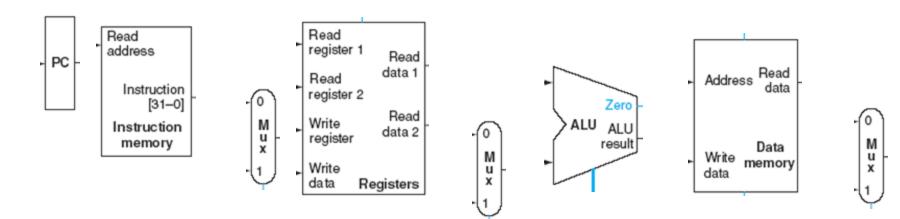

### In Class Exercise Question

- Design a simplified MIPS processor that supports only addi.

Assume the control signals have been generated and only the data path needs to be designed.

- addi \$rt, \$rs, imm

- opcode (6 bits) rs (5 bits) rt (5 bits) imm (16 bits)

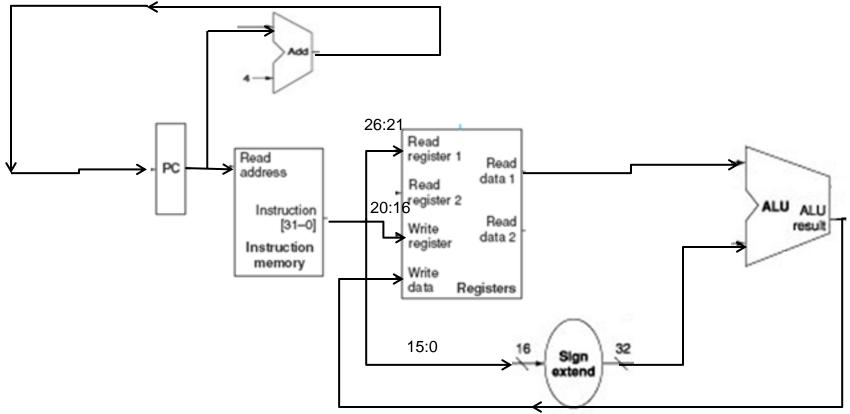

#### In Class Exercise Answer

- Design a simplified MIPS processor that supports only addi.

Assume the control signals have been generated and only the data path needs to be designed.

- addi \$rt, \$rs, imm

- opcode (6 bits) rs (5 bits) rt (5 bits) imm (16 bits)

### Iw & sw?

### Data path only for lw and sw (answer)

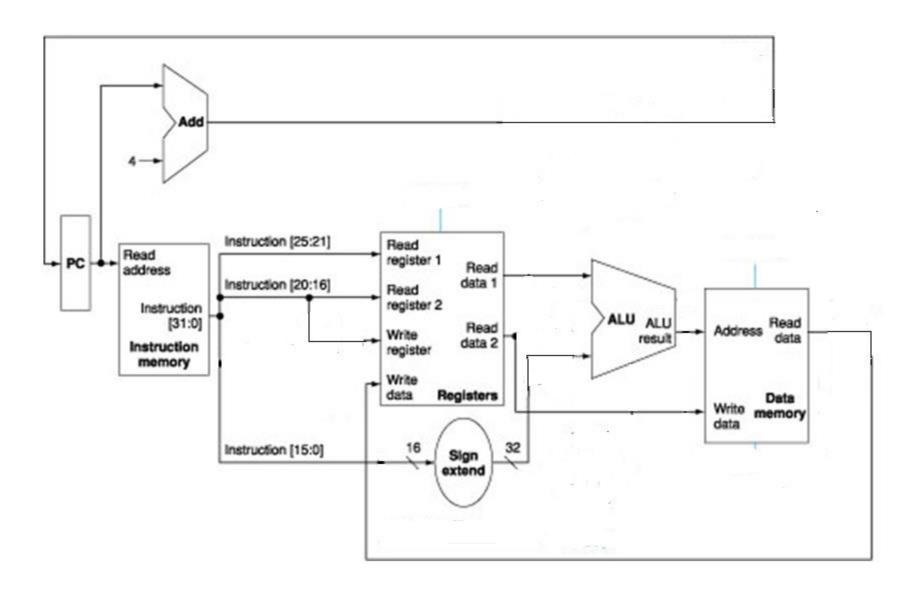

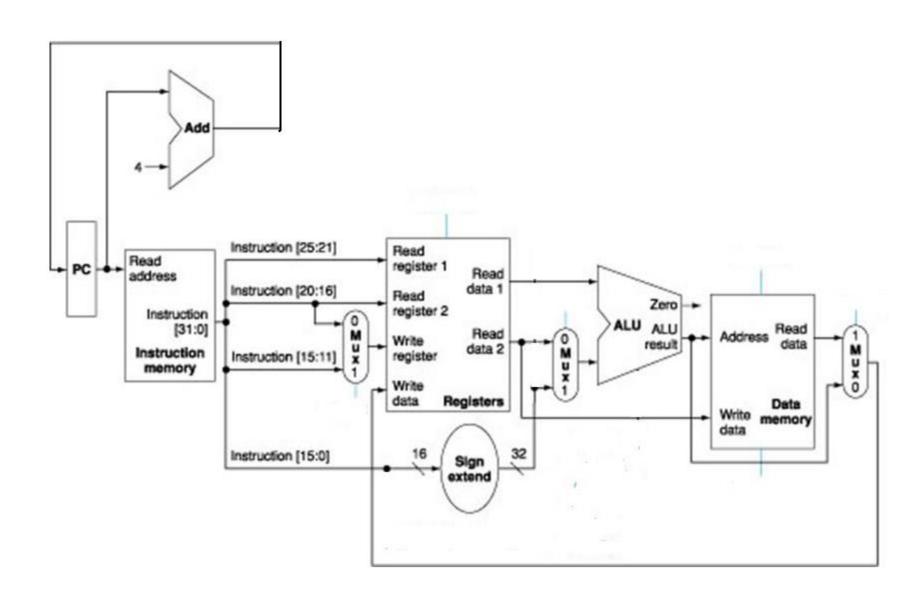

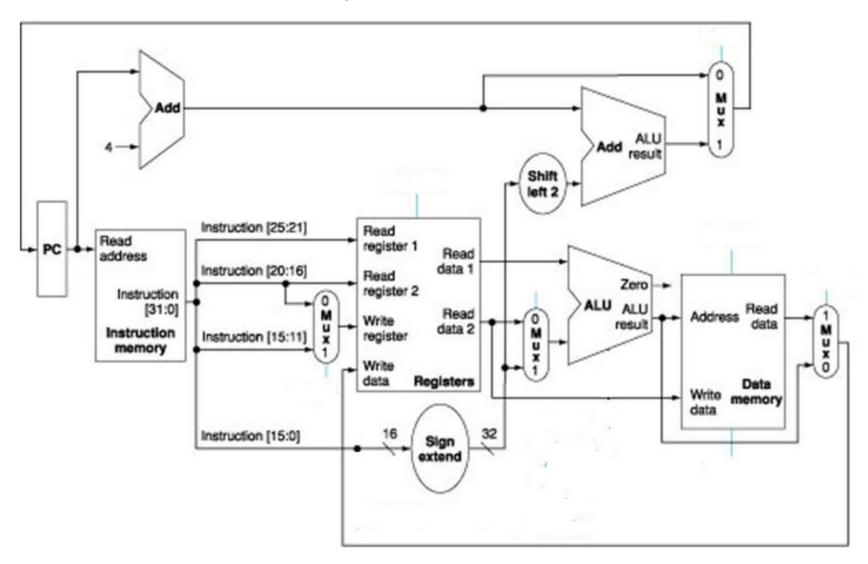

# Data path for both R-type and memory-type instructions

add \$rd, \$rs, \$rt, format: opcode (6 bits) rs (5 bits) rt (5 bits) rd (5 bits) 00000 funct (6 bits) lw \$rt, offset\_value(\$rs): opcode (6 bits) rs (5 bits) rt (5 bits) offset (16 bits) sw \$rt, offset\_value(\$rs): opcode (6 bits) rs (5 bits) rt (5 bits) offset (16 bits)

# Data path for both R-type and memory-type instructions

add \$rd, \$rs, \$rt, format: opcode (6 bits) rs (5 bits) rt (5 bits) rd (5 bits) 00000 funct (6 bits) lw \$rt, offset\_value(\$rs): opcode (6 bits) rs (5 bits) rt (5 bits) offset (16 bits) sw \$rt, offset\_value(\$rs): opcode (6 bits) rs (5 bits) rt (5 bits) offset (16 bits)

#### **Answer**

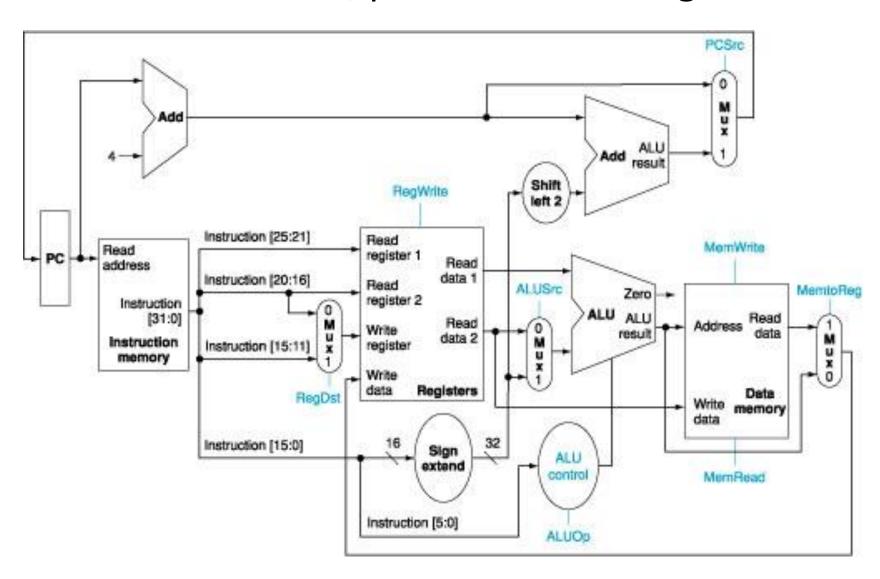

# Datapath for R-type, memory, and branch operations

# Datapath for R-type, memory, and branch operations (Answer)

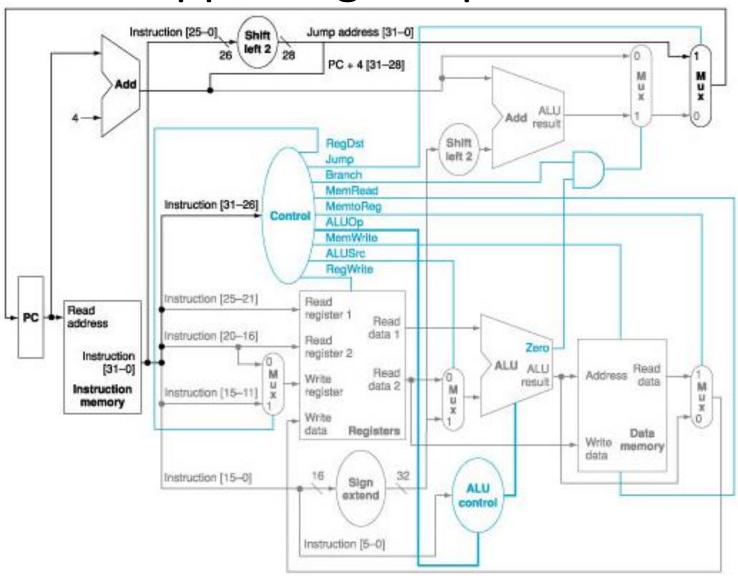

# Datapath for Memory, R-type and Branch Instructions, plus the control signals

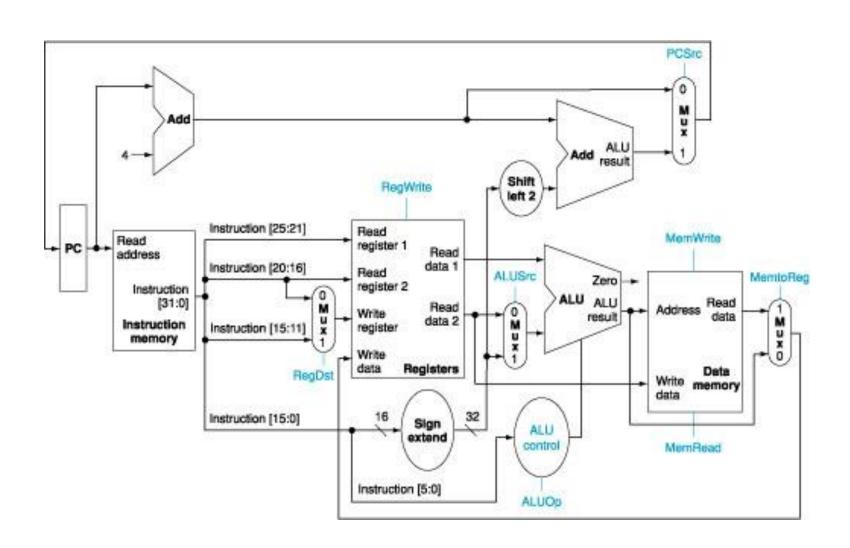

### Jump Instruction

- Jump instruction seems easy to implement

- We just need to replace the lower 28 bits of the

PC with the lower 26 bits of the instruction shifted

by 2 bits

- The shift is achieved by simply concatenating 00 to the jump offset

### Implementing Jumps

- The one we have supports arithmetic/logic instructions, branch instructions, load and store instructions

- We need also to support the jump instruction

– What are the changes we need to make?

### Add j?

### Supporting Jump Instruction

### In Class Exercise